PLL

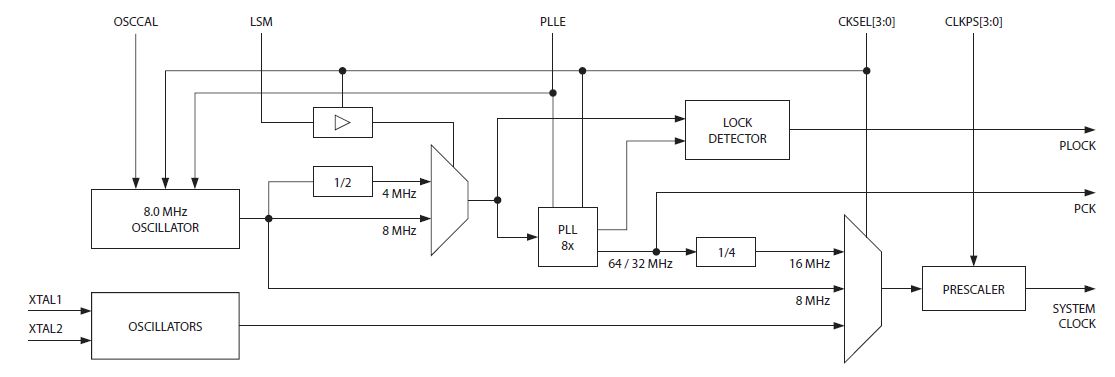

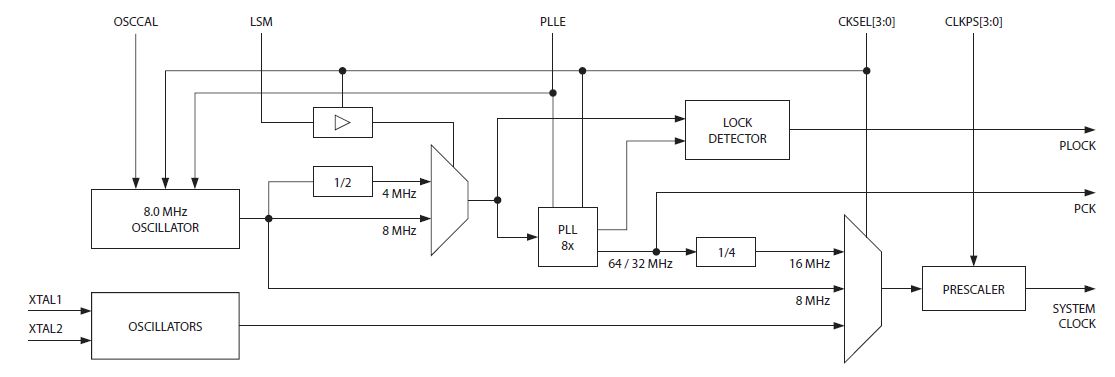

ATiny85は内部8MHzのRC発振器を持っています。この周波数から8倍の周波数のクロックを作るのがPLL(Phase Locked Loop)です。PLLはこの8MHzの基準信号と、ループ内の発振器からの出力との位相差が一定になるよう、ループ内発振器にフィードバック制御をかけて発振をさせる発振回路です。

PLLの設定

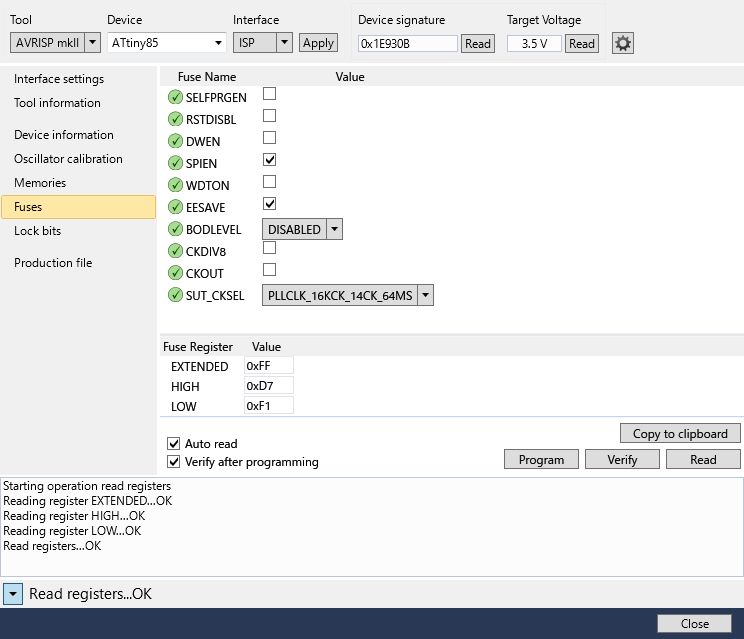

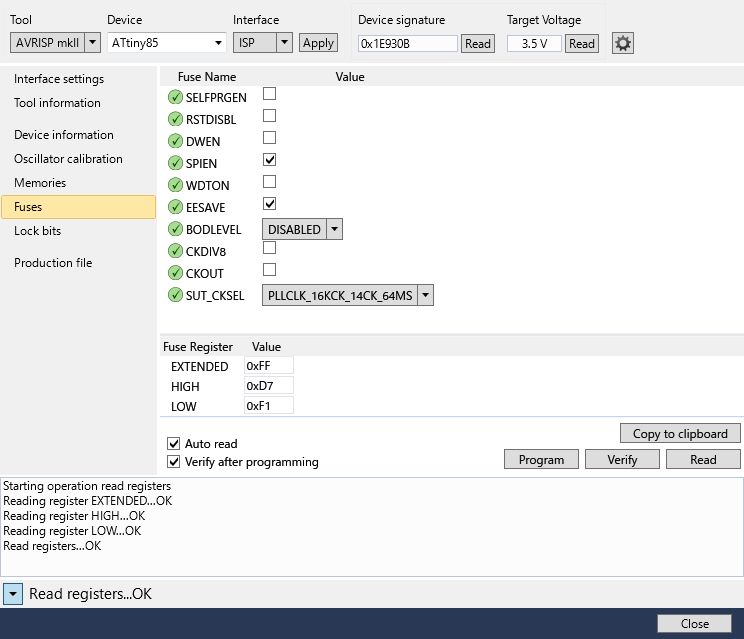

プログラムの書き込みと同時にクロックをどのようにするかを設定します。CKDIV8のチェックを外します。これはあらかじめ1/8に分周する設定ですが、高速で使用するためチェックを外します。SUT_CKSELはPLLを選びます。その他の16KCKなどは今回の場合余り影響がないと思います。

- LSM: Low Speed Mode 半分のスピードにする。ここでは用いない

- PCKE: PCK Enable 非同期クロックモード、カウンター1/タイマー1に64MHzの発振器が使用可能になる。PLLEが1でないと使えない。

- PLLE: PLL Enable PLLが開始される

- PLOCK: PLL Lock Detector 読み取りのみ PLLがロックされていると1になる

従って、ここで用いる設定としては0x06となる。

このように設定して、PCK=64MHz、SYSTEM CLOCK=16MHzでこれとCLKIOと等しくなるように後で設定します。